# DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING LAB MANUAL

# **VLSI LAB**

Semester - VII

Subject - VLSI LAB

# LIST OF EXPERIMENTS & SCHEDULE

| Exp. No. | Title                                      | Week No. |

|----------|--------------------------------------------|----------|

| S. No    | Experiments                                | Page. No |

| 1        | Design of Logic gates                      | 1        |

| 2        | Design of Binary Adders                    | 2        |

| 3        | Design of Multiplexers and De-multiplexers | 3        |

| 4        | Design of Encoders and Decoders            | 4        |

| 5        | Flip Flops                                 | 5        |

| 6        | Counters                                   | 6        |

| 7        | Bitwise Operators Using 8051               | 7        |

| 8        | Toggle a Port bit in 8051                  | 8        |

| 9        | Delay Operators in 8051                    | 9        |

|          |                                            |          |

# **Introduction to Combinational Circuit Design**

# **EXP:1** Design of Logic gates

#### Introduction

The purpose of this experiment is to simulate the behavior of several of the basic logic gates and you will connect several logic gates together to create simple digital model.

## **Software tools Requirement**

Equipments:

Computer with Modelsim Software

Specifications:

HP Computer P4 Processor – 2.8 GHz, 2GB RAM, 160 GB Hard Disk

Softwares: Modelsim - 5.7c, Xilinx - 6.1i.

#### Algorithm

STEP 1: Open ModelSim XE II / Starter 5.7C

STEP 2: File -> Change directory -> D:\<register number>

STEP 3: File -> New Library -> ok

STEP 4: File -> New Source -> Verilog

STEP 5: Type the program

STEP 6: File -> Save -> <filename.v>

STEP 7: Compile the program

STEP 8: Simulate -> expand work -> select file -> ok

STEP 9: View -> Signals

STEP 10: Select values -> Edit -> Force -> input values

STEP 11: Add -> Wave -> Selected signals -> Run

STEP 12: Change input values and run again

# **Logic Gates and their Properties**

| Gate | Description                                                                                              | Truth 7             | able               | Logic Symbol | Pin Diagram                                                                                                         |

|------|----------------------------------------------------------------------------------------------------------|---------------------|--------------------|--------------|---------------------------------------------------------------------------------------------------------------------|

| OR   | The output is active high if any one of the input is in active high state, Mathematically, $Q = A + B$   | A B 0 0 0 1 1 0 1 1 | Output Q 0 1 1 1 1 | A A+B        | 7432<br>1 vcc 14<br>2 vcc 14<br>2 13<br>3 12<br>4 11<br>5 0 9<br>7 GND 8                                            |

| AND  | The output is active high only if both the inputs are in active high state, Mathematically, $Q = A.B$    | A B 0 0 1 1 1 0 1 1 | Output Q 0 0 0 1   | A AND AB     | 7408 1                                                                                                              |

| NOT  | In this gate the output is opposite to the input state, Mathematically, Q = A                            | A<br>0<br>1         | Output<br>Q<br>1   | A NOT        | 7404 1                                                                                                              |

| NOR  | The output is active high only if both the inputs are in active low state, Mathematically, $Q = (A+B)$ , | A B 0 0 1 1 1 0 1 1 | Output Q 1 0 0 0   | A DO A+B     | 7402<br>1 VCC 14<br>2 VCC 14<br>2 VCC 14<br>13<br>3 12<br>4 VCC 16<br>10<br>6 S S S S S S S S S S S S S S S S S S S |

| NAND | The output is active high only if any one of the input is in active low state, Mathematically, $Q = (A.B)^{3}$    | A<br>0<br>0<br>1 | B<br>0<br>1<br>0      | Output Q 1 1 1 1 0 | A AB NAND | 7400<br>1 |

|------|-------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|--------------------|-----------|-----------|

| XOR  | The output is active high only if any one of the input is in active high state, Mathematically, $Q = A.B' + B.A'$ | A<br>0<br>0<br>1 | B<br>0<br>1<br>0<br>1 | Output Q 0 1 1 0   | A A@B     | 7486      |

# **Pre lab Questions**

- 1. What is truth table?

- 2. Which gates are called universal gates?

- 3. What is the difference b/w HDL and software language?

- 4. Define identifiers.

- 5. A basic 2-input logic circuit has a HIGH on one input and a LOW on the other input, and the output is HIGH. What type of logic circuit is it?

- 6. A logic circuit requires HIGH on all its inputs to make the output HIGH. What type of logic circuit is it?

- 7. Develop the truth table for a 3-input AND gate and also determine the total number of possible combinations for a 4-input AND gate.

# **VERILOG Program**

# a) AND Gate

| Structural Model     | <b>Data Flow Model</b> | BehaviouralModel      |

|----------------------|------------------------|-----------------------|

| moduleandstr(x,y,z); | moduleanddf(x,y,z);    | module andbeh(x,y,z); |

| inputx,y;            | inputx,y;              | input x,y;            |

| output z;            | output z;              | output z;             |

| and $g1(z,x,y)$ ;    | assign z=(x&y);        | reg z;                |

| endmodule            | endmodule              | always @(x,y)         |

|                      |                        | z=x&y                 |

|                      |                        | endmodule             |

# b) NAND Gate

| Structural Model      | Data Flow Model      | BehaviouralModel       |

|-----------------------|----------------------|------------------------|

| modulenandstr(x,y,z); | modulenanddf(x,y,z); | module nandbeh(x,y,z); |

| inputx,y;             | inputx,y;            | input x,y;             |

| output z;             | output z;            | output z;              |

| nand $g1(z,x,y)$ ;    | assign $z=!(x&y);$   | reg z;                 |

| endmodule             | endmodule            | always @(x,y)          |

|                       |                      | z=!(x&y);              |

|                       |                      | endmodule              |

# c) OR Gate

| Structural Model     | Data Flow Model        | BehaviouralModel     |

|----------------------|------------------------|----------------------|

| module orstr(x,y,z); | module $ordf(x,y,z)$ ; | module orbeh(x,y,z); |

| inputx,y;            | inputx,y;              | input x,y;           |

| output z;            | output z;              | output z;            |

| or $g1(z,x,y)$ ;     | assign $z=(x y)$ ;     | reg z;               |

| endmodule            | endmodule              | always @(x,y)        |

|                      |                        | z=x y;               |

|                      |                        | endmodule            |

# d) NOR Gate

| Structural Model     | Data Flow Model     | BehaviouralModel     |

|----------------------|---------------------|----------------------|

| modulenorstr(x,y,z); | modulenordf(x,y,z); | Modulenorbeh(x,y,z); |

| inputx,y;            | inputx,y;           | input x,y;           |

| output z;            | output z;           | output z;            |

| nor $g1(z,x,y)$ ;    | assign $z=!(x y);$  | reg z;               |

| endmodule            | endmodule           | always @(x,y)        |

|                      |                     | z=!(x y);            |

|                      |                     | endmodule            |

#### e) XOR Gate

| Structural Model      | Data Flow Model      | BehaviouralModel      |

|-----------------------|----------------------|-----------------------|

| module xorstr(x,y,z); | module xordf(x,y,z); | module xorbeh(x,y,z); |

| inputx,y;             | inputx,y;            | input x,y;            |

| output z;             | output z;            | output z;             |

| xor g1(z,x,y);        | assign $z=(x^y)$ ;   | reg z;                |

| endmodule             | endmodule            | always @(x,y)         |

|                       |                      | z=x^y;                |

|                       |                      | endmodule             |

#### f) XNOR Gate

| Structural Model      | Data Flow Model      | BehaviouralModel       |

|-----------------------|----------------------|------------------------|

| modulexnorstr(x,y,z); | modulexnordf(x,y,z); | module xnorbeh(x,y,z); |

| inputx,y;             | inputx,y;            | input x,y;             |

| output z;             | output z;            | output z;              |

| xnor g1(z,x,y);       | assign $z=!(x^y);$   | reg z;                 |

| endmodule             | endmodule            | always @(x,y)          |

|                       |                      | $z=!(x^y);$            |

|                       |                      | endmodule              |

## g) NOT Gate

| Structural Model    | Data Flow Model    | BehaviouralModel    |

|---------------------|--------------------|---------------------|

| module notstr(x,z); | module notdf(x,z); | module notbeh(x,z); |

| input x;            | input x;           | input x;            |

| output z;           | output z;          | output z;           |

| not $g1(z,x)$ ;     | assign $z=!x;$     | reg z;              |

| endmodule           | endmodule          | always @(x)         |

|                     |                    | z=!x;               |

|                     |                    | endmodule           |

# **Post lab Questions**

- 1. What is meant by ports?

- 2. Write the different types of port modes.

- 3. What are different types of operators?

- 4. What is difference b/w <= and := operators?

- 5. What is meant by simulation?

- 6. How to give the inputs in modelsim software.

### Lab Report

Each individual will be required to submit a lab report. Use the format specified in the "Lab Report Requirements" document available on the class web page. Be sure to include the following items in your lab report:

Lab cover sheet with staff verification sign.

Answer the pre-lab questions

Complete VERILOG code design for all logic gates and output signal waveforms

Answer the post-lab questions

## 1.6 Grading

Pre-lab Work 20 points

Lab Performance 30 points

Post-lab Work 20 points

Lab report 30 points

For the lab performance - at a minimum, demonstrate the operation of all the logic gates to your staff incharge:

The lab report will be graded as follows (for the 30 points):

VERILOG code for each logic gates 15 points

Output signal waveform for all logic gates and its truth table 15 points

# **EXP:2** Design of Binary Adders

#### Introduction

The purpose of this experiment is to introduce the design of simple combinational circuits, in this case half adders, half subtractors, full adders and full subtractors.

Software tools Requirement

Equipments:

Computer with Modelsim Software

Specifications:

HP Computer P4 Processor – 2.8 GHz, 2GB RAM, 160 GB Hard Disk

Softwares: Modelsim - 5.7c, Xilinx - 6.1i.

#### **Algorithm**

STEP 1: Open ModelSim XE II / Starter 5.7C

STEP 2: File -> Change directory -> D:\<register number>

STEP 3: File -> New Library -> ok

STEP 4: File -> New Source -> Verilog

STEP 5: Type the program

STEP 6: File -> Save -> <filename.v>

STEP 7: Compile the program

STEP 8: Simulate -> expand work -> select file -> ok

STEP 9: View -> Signals

STEP 10: Select values -> Edit -> Force -> input values

STEP 11: Add -> Wave -> Selected signals -> Run

STEP 12: Change input values and run again

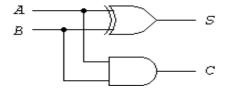

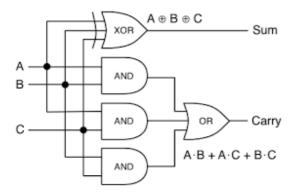

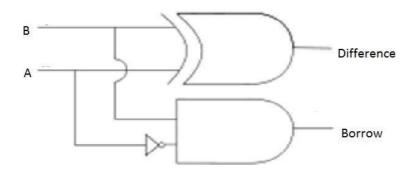

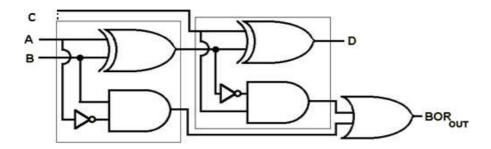

#### Logic Diagram

Figure 2.2.1Half adder

Figure 2.2.2 Full adder

Figure 2.2.3Halfsubtractor

Figure 2.2.4 Full subtractor

# **Pre lab Questions**

- 1. What is meant by combinational circuits?

- 2. Write the sum and carry expression for half and full adder.

- 3. Write the difference and borrow expression for half and full subtractor.

- 4. What is signal? How it is declared?

# **VERILOG Program**

# **HALF ADDER:**

| Structural model              | Dataflow model               | Behaviouralmodel               |

|-------------------------------|------------------------------|--------------------------------|

| modulehalfaddstr(sum,carry,a, | modulehalfadddf(sum,carry,a, | modulehalfaddbeh(sum,carry,a,b |

| b);                           | b);                          | );                             |

| outputsum,carry;              | outputsum,carry;             | outputsum,carry;               |

| inputa,b;                     | inputa,b;                    | inputa,b;                      |

| xor(sum,a,b);                 | assign sum = $a \wedge b$ ;  | regsum,carry;                  |

| and(carry,a,b);               | assign carry=a&b             | always @(a,b);                 |

| endmodule                     | endmodule                    | $sum = a \wedge b;$            |

|                               |                              | carry=a&b                      |

|                               |                              | endmodule                      |

#### **FULL ADDER:**

| Structural model             | Dataflow model                    | Behaviouralmodel                   |

|------------------------------|-----------------------------------|------------------------------------|

| module                       | modulefulladddf(sum,carry,a,b,c); | modulefulladdbeh(sum,carry,a,b,c); |

| fulladdstr(sum,carry,a,b,c); | outputsum,carry;                  | outputsum,carry;                   |

| outputsum,carry;             | inputa,b,c;                       | inputa,b,c;                        |

| inputa,b,c;                  | assign sum = $a \wedge b c$ ;     | regsum,carry;                      |

| xor g1(sum,a,b,c);           | assign carry=(a&b)   (b&c)        | always @ (a,b,c)                   |

| and $g2(x,a,b)$ ;            | (c&a);                            | $sum = a ^ b^c;$                   |

| and g3(y,b,c);               | endmodule                         | carry=(a&b)   (b&c)   (c&a);       |

| and $g4(z,c,a)$ ;            |                                   | endmodule                          |

| or g5(carry,x,z,y);          |                                   |                                    |

| endmodule                    |                                   |                                    |

# **HALF SUBTRACTOR:**

| Structural model                 | Dataflow Model                  | BehaviouralModel                 |

|----------------------------------|---------------------------------|----------------------------------|

| modulehalfsubtstr(diff,borrow,a, | modulehalfsubtdf(diff,borrow,a, | modulehalfsubtbeh(diff,borrow,a, |

| b);                              | b);                             | b);                              |

| outputdiff,borrow;               | outputdiff,borrow;              | outputdiff,borrow;               |

| inputa,b;                        | inputa,b;                       | inputa,b;                        |

| xor(diff,a,b);                   | assign diff = a ^ b;            | regdiff,borrow;                  |

| and( borrow,~a,b);               | assign borrow=(~a&b);           | always @(a,b)                    |

| endmodule                        | endmodule                       | $diff = a \wedge b;$             |

|                                  |                                 | borrow=(~a&b);                   |

|                                  |                                 | endmodule                        |

|                                  |                                 |                                  |

#### **FULL SUBTRACTOR:**

| Structural model               | Dataflow Model                                | BehaviouralModel                       |

|--------------------------------|-----------------------------------------------|----------------------------------------|

| module                         | modulefullsubtdf(diff,borrow,a,b,c)           | modulefullsubtbeh(diff,borrow,a,b,c)   |

| fullsubtstr(diff,borrow,a,b,c) | ;                                             | •                                      |

| ;                              | outputdiff,borrow;                            | outputdiff,borrow;                     |

| outputdiff,borrow;             | inputa,b,c;                                   | inputa,b,c;                            |

| inputa,b,c;                    | assign diff = a^b^c;                          | outputdiff,borrow;                     |

| wire a0,q,r,s,t;               | assign borrow= $(\sim a\&b) (\sim (a^b)\&c);$ | always@(a,b,)                          |

| not(a0,a);                     | endmodule                                     | $diff = a^b^c;$                        |

| xor(x,a,b);                    |                                               | borrow= $(\sim a\&b) (\sim (a^b)\&c);$ |

| xor(diff,x,c);                 |                                               | endmodule                              |

| and $(y,a0,b)$ ;               |                                               |                                        |

| and $(z,\sim x,c)$ ;           |                                               |                                        |

| or(borrow,y,z);                |                                               |                                        |

| endmodule                      |                                               |                                        |

#### **Post lab Questions**

- 1. What are the signal assignment statements?

- 2. What are the concurrent statements?

- 3. Write short notes on : a) Process statement b) Block statement

- 4. Write about sequential statements.

- 5. What is the difference b/w high impedance state of the signal(Z) and unknown state of the signal(X).

#### Lab Report

Each individual will be required to submit a lab report. Use the format specified in the "Lab Report Requirements" document available on the class web page. Be sure to include the following items in your lab report:

Lab cover sheet with staff verification sign.

Answer the pre-lab questions

Complete VERILOG code design for all logic gates and output signal waveforms

Answer the post-lab questions

# Grading

Pre-lab Work 20 points

Lab Performance 30 points

Post-lab Work 20 points

Lab report 30 points

For the lab performance - at a minimum, demonstrate the operation of all the logic gates to your staff incharge

The lab report will be graded as follows (for the 30 points):

VERILOG code for each experiments 15 points

Output signal waveform for all experiments and its truth table 15 points

# **EXP:3** Design of Multiplexers and Demultiplexers

#### Introduction

The purpose of this experiment is to write and simulate a VERILOG program for Multiplexers and Demultiplexers.

## **Software tools Requirement:**

Equipments:

Computer with Modelsim Software

Specifications:

HP Computer P4 Processor – 2.8 GHz, 2GB RAM, 160 GB Hard Disk

Softwares: Modelsim - 5.7c, Xilinx - 6.1i.

#### Algorithm

STEP 1: Open ModelSim XE II / Starter 5.7C

STEP 2: File -> Change directory -> D:\<register number>

STEP 3: File -> New Library -> ok

STEP 4: File -> New Source -> Verilog

STEP 5: Type the program

STEP 6: File -> Save -> <filename.v>

STEP 7: Compile the program

STEP 8: Simulate -> expand work -> select file -> ok

STEP 9: View -> Signals

STEP 10: Select values -> Edit -> Force -> input values

STEP 11: Add -> Wave -> Selected signals -> Run

STEP 12: Change input values and run again

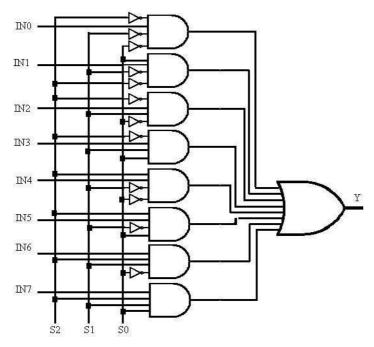

# Logic Diagram

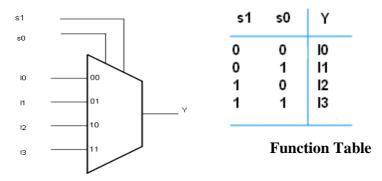

Figure 3.2.1 4:1 Multiplexer Block diagram

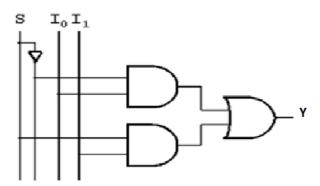

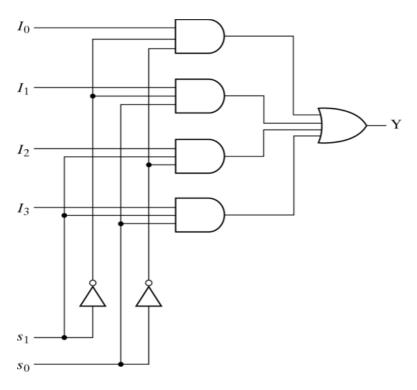

Logic Diagram

Figure 3.2.3 2:1 Multiplexer

Figure 3.2.4 4:1 Multiplexer

# **VERILOG Program**

# **Multiplexers 2:1 MUX**

| Structural Model            | Dataflow Model                     | BehaviouralModel            |

|-----------------------------|------------------------------------|-----------------------------|

| module mux21str(i0,i1,s,y); | module mux21df(i0,i1,s,y);         | module mux21beh(i0,i1,s,y); |

| input i0,i1,s;              | input i0,i1,s;                     | input i0,i1,s;              |

| output y;                   | output y;                          | output y;                   |

| wire net1,net2,net3;        | assign y = $(i0&(\sim s)) (i1&s);$ | reg y;                      |

| not g1(net1,s);             | endmodule                          | always@(i0,i1)              |

| and g2(net2,i1,s);          |                                    | begin                       |

| and g3(net3,i0,net1);       |                                    | if(s==0) y=i1;              |

| or g4(y,net3,net2);         |                                    | if(s==1)y=i0;               |

| endmodule                   |                                    | end                         |

|                             |                                    | endmodule                   |

# 4:1 MUX

| Structural Model                    | Dataflow Model                   | BehaviouralModel             |

|-------------------------------------|----------------------------------|------------------------------|

| module                              | module                           | module mux41beh(in,s,y);     |

| mux41str(i0,i1,i2,i3,s0,s1,y);      | mux41df(i0,i1,i2,i3,s0,s1,y);    | output y;                    |

| input i0,i1,i2,i3,s0,s1;            | input i0,i1,i2,i3,s0,s1;         | input [3:0] in ;             |

| wire a,b,c,d;                       | output y;                        | input [1:0] s ;              |

| output y;                           | assign                           | reg y;                       |

| and $g1(a,i0,s0,s1);$               | $y=((i0&(\sim(s0))&(\sim(s1))) $ | always @ (in,s)              |

| and $g2(b,i1,(\sim s0),s1);$        | (i1&(~(s0))&s1)                  | begin                        |

| and $g3(c,i2,s0,(\sim s1));$        | (i2&s0&(~(s1)))                  | if $(s[0]==0&s[1]==0)$       |

| and $g4(d,i3,(\sim s0),(\sim s1));$ | (i3&s0&s1);                      | y = in[3];                   |

| or(y,a,b,c,d);                      | endmodule                        | else if $(s[0]==0&s[1]==1)$  |

| endmodule                           |                                  | y = in[2];                   |

|                                     |                                  | else if $(s[0]l==1&s[1]==0)$ |

|                                     |                                  | y = in[1];                   |

|                                     |                                  | else                         |

|                                     |                                  | y = in[0];                   |

|                                     |                                  | end                          |

|                                     |                                  | endmodule                    |

# Logic Diagram

Figure 3.2.5 8:1 Multiplexer

# **VERILOG Program**

# 8:1 MUX

| Structural Model                           | Dataflow Model          | BehaviouralModel                       |

|--------------------------------------------|-------------------------|----------------------------------------|

| modulemux81str(i0,i1,i2,i3,i4,i5,i6,i7,s0, | modulemux81df(y,i,s);   | modulemux81beh(s,i0,i1,i2,i3,i4,i5,i   |

| s1,s2,y);                                  | output y;               | 6,i7,y);                               |

| input i0,i1,i2,i3,i4,i5,i6,i7,s0,s1,s2;    | input [7:0] i;          | input [2:0] s;                         |

| wire a,b,c,d,e,f,g,h;                      | input [2:0] s;          | input i0,i1,i2,i3,i4,i5,i6,i7;         |

| output y;                                  | wire se1;               | regy;                                  |

| and g1(a,i7,s0,s1,s2);                     | assign                  | always@(i0,i1,i2,i3,i4,i5,i6,i7,s) beg |

| and g2(b,i6,(~s0),s1,s2);                  | se1=(s[2]*4) (s[1]*2) ( | in                                     |

| and g3(c,i5,s0,(~s1),s2);                  | s[0]);                  | case(s) begin                          |

| and $g4(d,i4,(\sim s0),(\sim s1),s2);$     | assign y=i[se1];        | 3'd0:MUX_OUT=i0;                       |

| and g5(e,i3,s0,s1,(~s2));                  | endmodule               | 3'd1:MUX_OUT=i1;                       |

| and g6(f,i2,(~s0),s1,(~s2));               |                         | 3'd2:MUX_OUT=i2;                       |

| and $g7(g,i1,s0,(\sim s1),(s2));$          |                         | 3'd3:MUX_OUT=i3;                       |

| and g8(h,i0,(~s0),(~s1),(~s2));            |                         | 3'd4:MUX_OUT=i4;                       |

| or(y,a,b,c,d,e,f,g,h);                     |                         | 3'd5:MUX_OUT=i5;                       |

| endmodule                                  |                         | 3'd6:MUX_OUT=i6;                       |

|                                            |                         | 3'd7:MUX_OUT=i7;                       |

|                                            |                         | endcase                                |

|                                            |                         | end                                    |

|                                            |                         | endmodule endmodule                    |

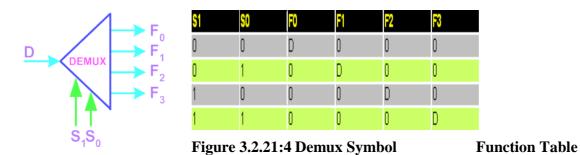

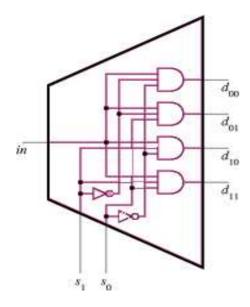

# Logic Diagram

Figure 3.2.6 1:4 Demultiplexer

Figure 3.2.7 1:8 Demultiplexer

# **VERILOG Program**

# **1:4 DEMUX**

| Structural Model                  | Dataflow Model                                               | BehaviouralModel                   |

|-----------------------------------|--------------------------------------------------------------|------------------------------------|

| module                            | module demux14df(                                            | module demux14beh(                 |

| demux14str(in,d0,d1,d2,d3,s0,s1); | in,d0,d1,d2,d3,s0,s1);                                       | din,sel,dout );                    |

| output d0,d1,d2,d3;               | output d0,d1,d2,3;                                           | output [3:0] dout;                 |

| input in,s0,s1;                   | input in,s0,s1;                                              | reg [3:0] dout;                    |

| and g1(d0,in,s0,s1);              | assign $s0 = in \& (\sim s0) \&$                             | input din;                         |

| and g2(d1,in,(~s0),s1);           | (~s1);                                                       | wire din;                          |

| and g3(d2,in,s0,(~s1));           | assign $d1 = \text{in } \& (\sim \text{s0}) \& \text{s1};$   | input [1:0] sel;                   |

| and g4(d3,in,(~s0),(~s1));        | assign $d2 = \text{in } \& \text{ so } \& (\sim \text{s1});$ | wire [1:0] sel;                    |

| endmodule                         | assign d3= in & s0 & s1;                                     | always @ (din or sel) begin        |

|                                   | endmodule                                                    | case (sel)                         |

|                                   |                                                              | $0: dout = \{din, 3'b000\};$       |

|                                   |                                                              | $1 : dout = \{1'b0, din, 2'b00\};$ |

|                                   |                                                              | $2 : dout = \{2'b00, din, 1'b0\};$ |

|                                   |                                                              | default : dout =                   |

|                                   |                                                              | {3'b000,din};                      |

|                                   |                                                              | endcase                            |

|                                   |                                                              | end                                |

|                                   |                                                              | endmodule                          |

#### **1:8 DEMUX**

| Structural Model              | Dataflow Model                                                                   | BehaviouralModel   |

|-------------------------------|----------------------------------------------------------------------------------|--------------------|

| module                        | module                                                                           | module             |

| demux18str(in,s0,s1,s2,d0,d1  | demux18df(in,s0,s1,s2,i0,d1,d2,d3,d                                              | demux18beh(i, sel, |

| ,d2,d3,d4,d5,d6,d7);          | 4,d5,d6,d7);                                                                     | y);                |

| input in,s0,s1,s2;            | input in,s0,s1,s2;                                                               | input i;           |

| output                        | output d0,d1,d2,d3,d4,d5,d6,d7;                                                  | input [2:0] sel;   |

| d0,d1,d2,d3,d4,d5,d6,d7;      | assign $d0 = \text{in \& s0 \& s1 \& s2};$                                       | output [7 :0] y ;  |

| and g1(d0,in,s0,s1,s2);       | assign $d1 = \text{in } \& (\sim s0) \& s1 \& s2;$                               | reg [7:0] y;       |

| and g2(d1,in,(~s0),s1,s2);    | assign $d2 = in \& s0 \& (\sim s1) \& s2;$                                       | always@(i,sel)     |

| and g3(d2,in,s0,(~s1),s2);    | assign $d3 = in \& (\sim s0) \& (\sim s1) \& s2;$                                | begin              |

| and g4(d3,in,(~s0),(~s1),s2); | assign $d4 = in \& s0 \& s1 \& (\sim s2);$                                       | y=8'd0;            |

| and g5(d4,in,s0,s1,(~s2));    | assign $d5 = in \& (\sim s0) \& s1 \& (\sim s2);$                                | case(sel)          |

| and g6(d5,in,(~s0),s1,(~s2)); | assign $d6 = \text{in } \& \text{ s0 } \& (\sim \text{s1}) \& (\sim \text{s2});$ | 3'd0:y[0]=i;       |

| and g7(d6,in,s0,(~s1),(~s2)); | assign $d7 = in \& (\sim s0) \& (\sim s1) \&$                                    | 3'd1:y[1]=i;       |

| and                           | (~s2);                                                                           | 3'd2:y[2]=i;       |

| g8(d7,in,(~s0),(~s1),(~s2));  | endmodule                                                                        | 3'd3:y[3]=i;       |

| endmodule                     |                                                                                  | 3'd4:y[4]=i;       |

|                               |                                                                                  | 3'd5:y[5]=i;       |

|                               |                                                                                  | 3'd6:y[6]=i;       |

|                               |                                                                                  | default:y[7]=i;    |

|                               |                                                                                  | endcase            |

|                               |                                                                                  | end                |

|                               |                                                                                  | endmodule          |

|                               |                                                                                  |                    |

## **Post Lab questions**

- 1. Implement the function  $f(A,B,C)=\Sigma m(0,1,3,5,7)$  by using Mux.

- 2. Write the VERILOG code for the above design

- 3. Write the VERILOG code for full subtractor using Demux.

## Lab Report

Each individual will be required to submit a lab report. Use the format specified in the "Lab Report Requirements" document available on the class web page. Be sure to include the following items in your lab report:

Lab cover sheet with staff verification sign.

Answer the pre-lab questions

Complete VERILOG code design for all logic gates and output signal waveforms

Answer the post-lab questions

# Grading

Pre-lab Work 20 points

Lab Performance 30 points

Post-lab Work 20 points

Lab report 30 points

For the lab performance - at a minimum, demonstrate the operation of all the logic gates to your staff incharge

The lab report will be graded as follows (for the 30 points):

VERILOG code for each experiments 15 points

Output signal waveform for all experiments and its truth table 15 points

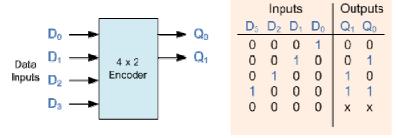

# **EXP:4** Design of Encoders and Decoders

#### Introduction

The purpose of this experiment is to introduce you to the basics of Encoders and Decoders. In this lab, you have to implement Priority Encoder and the Boolean function using Decoders.

Software tools Requirement

Equipments:

Computer with Modelsim Software

Specifications:

HP Computer P4 Processor – 2.8 GHz, 2GB RAM, 160 GB Hard Disk

Softwares: Modelsim - 5.7c, Xilinx - 6.1i.

#### **Algorithm**

STEP 1: Open ModelSim XE II / Starter 5.7C

STEP 2: File -> Change directory -> D:\<register number>

STEP 3: File -> New Library -> ok

STEP 4: File -> New Source -> Verilog

STEP 5: Type the program

STEP 6: File -> Save -> <filename.v>

STEP 7: Compile the program

STEP 8: Simulate -> expand work -> select file -> ok

STEP 9: View -> Signals

STEP 10: Select values -> Edit -> Force -> input values

STEP 11: Add -> Wave -> Selected signals -> Run

STEP 12: Change input values and run again

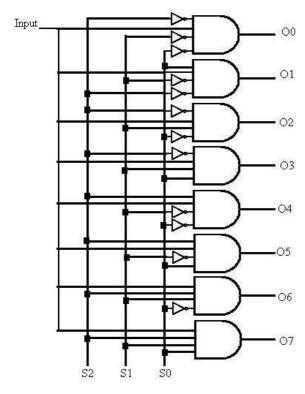

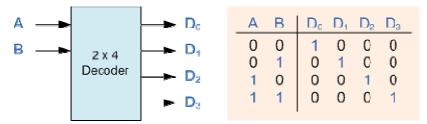

# **Logic Diagram**

Figure 4.1.1 4-to-2 bit Encoder

Figure 4.2.2 2-to-4 Binary Decoders

## **Prelab Questions**

- 1. What is difference b/w encoder and data selector.

- 2. What is the difference b/w decoder and data distributor.

- 3. Give the applications of encoder and decoder.

- 4. Write short notes on "with select" statement.

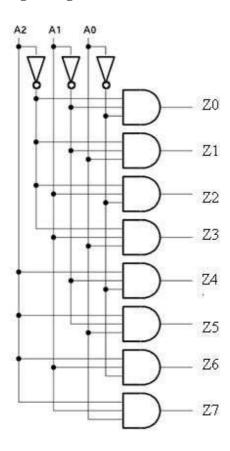

**Logic Diagram**

Figure 4.2.4 8:3 Encoder

# **VERILOG Program**

# 8:3 Encoder

| Structural Model                      | Data Flow Model                      | BehaviouralModel       |

|---------------------------------------|--------------------------------------|------------------------|

| Module                                | Module                               | module enc83beh        |

| enc83str(d0,d1,d2,d3,d4,d5,d6,d7,q0,q | enc83df(d0,d1,d2,d3,d4,d5,d6,d7,q0,q | (din,a,b,c);           |

| 1,q2);                                | 1,q2);                               | input [0:7]din;        |

| Input d0,d1,d2,d3,d4,d5,d6,d7;        | Input d0,d1,d2,d3,d4,d5,d6,d7;       | outputa,b,c;           |

| Output q0,q1,q2;                      | Output q0,q1,q2;                     | rega,b,c;              |

| Or $g1(q0,d1,d3,d5,d7)$ ;             | Assign q0=d1 d3 d5 d7;               | always@(din)           |

| Or g2(q1,d2,d3,d6,d7);                | Assign q1=d2 d3 d6 d7;               | case(din)              |

| Or g3(q2,d4,d5,d6,d7);                | Assign q2=d4 d5 d6 d7;               | 8'b10000000:begin      |

| Endmodule                             | Endmodule                            | a=1'b0;b=1'b0,c=1'b0;e |

|                                       |                                      | nd                     |

|                                       |                                      | 8'b01000000:be         |

|                                       |                                      | gin                    |

|                                       |                                      | a=1'b0;b=1'b0;c=1'b1;e |

|                                       |                                      | nd                     |

|                                       |                                      | 8'b00100000:be         |

|                                       |                                      | gin                    |

|                                       |                                      | a=1'b0;b=1'b1;c=1'b0;e |

|                                       |                                      | nd                     |

|                                       |                                      | 8'b00010000:be         |

|                                       |                                      | gin                    |

|                                       |                                      | a=1'b0;b=1'b1;c=1'b1;e |

|                                       |                                      | nd                     |

|                                       |                                      | 8'b10001000:be         |

|                                       |                                      | gin                    |

|                                       |                                      | a=1'b1;b=1'b0,c=1'b0;e |

|                                       |                                      | nd                     |

|                                       |                                      | 8'b10000100:be         |

|                                       |                                      | gin                    |

|                                       |                                      | a=1'b1;b=1'b0,c=1'b1;e |

|                                       |                                      | nd                     |

|                                       |                                      | 8'b10000010:be         |

|                                       |                                      | gin                    |

|                                       |                                      | a=1'b1;b=1'b1,c=1'b0;e |

|                                       |                                      | nd                     |

|                                       |                                      | 8'b10000001:be         |

|                                       |                                      | gin                    |

|                                       |                                      | a=1'b1;b=1'b1,c=1'b1;e |

|                                       |                                      | nd                     |

|                                       |                                      | endcase                |

|                                       |                                      | endmodule              |

|                                       |                                      |                        |

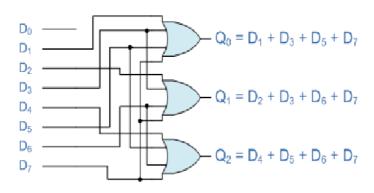

# Logic Diagram

Figure 4.2.5 3:8 Decoder

# **VERILOG Program**

# 3:8 Decoder

| Structural Model                              | Data Flow Model                    | BehaviouralModel             |

|-----------------------------------------------|------------------------------------|------------------------------|

| module                                        | module                             | module decoder38beh(sel,out1 |

| decoder38str(z0,z1,z2,z3,z4,z5,z6,z7,a0,a1,a2 | decoder38df(z,a0,a1,a2)            | );                           |

| );                                            | ;                                  |                              |

| output z0,z1,z2,z3,z4,z5,z6,z7;               | output [7:0] z;                    |                              |

| input a0,a1,a2;                               | input a0,a1,a2;                    | input [2:0] sel;             |

| not (s0,a0);                                  | $assign z[0] = \sim a0 \& \sim a1$ | outputreg [7:0] out1;        |

| not (s1,a1);                                  | & ~a2;                             |                              |

| not (s2,a2);                                  | assign $z[1] = \sim a0$ &          | always @(sel,out1)           |

| and (z0,s0,s1,s2);                            | ~a1& a2;                           | case (sel)                   |

| and (z1,a0,s1,s2);                            | assign $z[2] = ~a0\& a1\&$         | 3'b000 : out1 =              |

| and (z2,s0,a1,s2);                            | ~a2;                               | 8'b00000001;                 |

| and z3,a0,a1,s2);<br>and (z4,s0,s1,a2);<br>and (z5,a0,s1,a2);<br>and (z6,s0,a1,a2);<br>and (z7,a0,a1,a2);<br>endmodule | assign z[3] = ~a0& a1& a2;<br>assign z[4] = a0& ~a1& ~a2;<br>assign z[5] = a0& ~a1& a2;<br>assign z[6] = a0& a1& ~a2;<br>assign z[7] = a0& a1& a2;<br>endmodule | 3'b001: out1 = 8'b00000010; 3'b010: out1 = 8'b00000100; 3'b011: out1 = 8'b00001000; 3'b100: out1 = 8'b00100000; 3'b101: out1 = 8'b01000000; default: out1 = 8'b10000000; endcase endmodule |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## **Post Lab questions**

- 1. Implement full adder by using suitable decoder.

- 2. Write the VERILOG code for the above design

- 3. Write the VERILOG code for 3 bit Gray to binary code converter.

- 4. Write short notes on "test bench" with examples.

#### Lab Report

Each individual will be required to submit a lab report. Use the format specified in the "Lab Report Requirements" document available on the class web page. Be sure to include the following items in your lab report:

Lab cover sheet with staff verification sign.

Answer the pre-lab questions

Complete VERILOG code design for all logic gates and output signal waveforms

Answer the post-lab questions

# Grading

Pre-lab Work 20 points

Lab Performance 30 points

Post-lab Work 20 points

Lab report 30 points

For the lab performance - at a minimum, demonstrate the operation of all the logic gates to your staff incharge

The lab report will be graded as follows (for the 30 points):

VERILOG code for each experiments 15 points

Output signal waveform for all experiments and its truth table 15 point

# **EXP 5:** Flip Flops

#### Introduction

The purpose of this experiment is to introduce you to the basics of flip-flops. In this lab, you will test the behavior of several flip-flops and you will connect several logic gates together to create simple sequential circuits.

#### **Software tools Requirement**

Equipments:

Computer with Modelsim Software

Specifications:

HP Computer P4 Processor – 2.8 GHz, 2GB RAM, 160 GB Hard Disk

Softwares: Modelsim - 5.7c, Xilinx - 6.1i.

#### **Algorithm**

STEP 1: Open ModelSim XE II / Starter 5.7C

STEP 2: File -> Change directory -> D:\<register number>

STEP 3: File -> New Library -> ok

STEP 4: File -> New Source -> Verilog

STEP 5: Type the program

STEP 6: File -> Save -> <filename.v>

STEP 7: Compile the program

STEP 8: Simulate -> expand work -> select file -> ok

STEP 9: View -> Signals

STEP 10: Select values -> Edit -> Force -> input values

STEP 11: Add -> Wave -> Selected signals -> Run

STEP 12: Change input values and run again

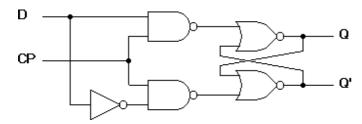

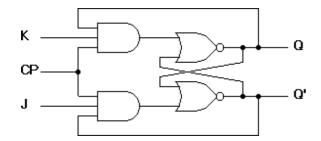

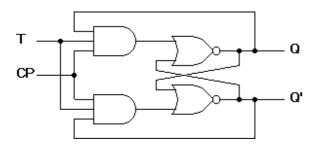

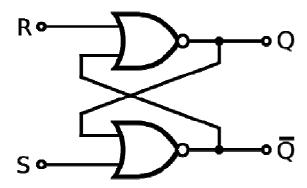

# 5.2 Flip-Flops Logic diagram and their properties

Flip-flops are synchronous bitable devices. The term synchronous means the output changes state only when the clock input is triggered. That is, changes in the output occur in synchronization with the clock.

A flip-flop circuit has two outputs, one for the normal value and one for the complement value of the stored bit. Since memory elements in sequential circuits are usually flip-flops, it is worth summarizing the behavior of various flip-flop types before proceeding further.

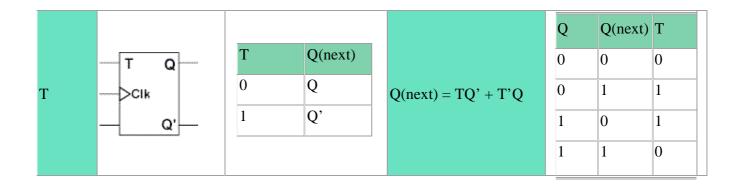

All flip-flops can be divided into four basic types: SR, JK, D and T. They differ in the number of inputs and in the response invoked by different value of input signals. The four types of flip-flops are defined in the Table 5.1. Each of these flip-flops can be uniquely described by its graphical symbol, its characteristic table, its characteristic equation or excitation table. All flip-flops have output signals Q and Q'.

| Flip-<br>Flop<br>Name | Flip-Flop Symbol   | Charac           | terist           | ic Table         | Characteristic Equation    | Excit            | ation Tab            | ole                   |                  |

|-----------------------|--------------------|------------------|------------------|------------------|----------------------------|------------------|----------------------|-----------------------|------------------|

| SR                    | S Q  CIk  R Q'     | S<br>0<br>0<br>1 | R<br>0<br>1<br>0 | Q(next) Q 0 1 ?  | Q(next) = S + R'Q $SR = 0$ | Q<br>0<br>0<br>1 | Q(next) 0 1 0 1      | S<br>0<br>1<br>0<br>X | R<br>X<br>0<br>1 |

| JK                    | J Q<br>CIk<br>K Q' | 0<br>0<br>1      | K 0 1 0 1        | Q(next) Q 0 1 Q' | Q(next) = JQ' + K'Q        | Q<br>0<br>0<br>1 | Q(next) 0 1 0 1      | J<br>0<br>1<br>X<br>X | X<br>X<br>1<br>0 |

| D                     | D Q  CIk  Q'       | D<br>0<br>1      |                  | Q(next) 0 1      | Q(next) = D                | Q<br>0<br>0<br>1 | Q(nex<br>0<br>1<br>0 | (at) E 0 1 0 1        |                  |

Table 5.2 Flip-flops and their properties

# 5.2 Logic Diagram

Figure 5.2.1 D- Flip Flop

Figure 5.2 .2 JK Flip Flop

Figure 5.2.3 T Flip Flop

Figure 5.2.4 T Flip Flop

# 5. 3 Pre-lab Questions

- 1. Describe the main difference between a gated S-R latch and an edge-triggered S-R flip-flop.

- 2. How does a JK flip-flop differ from an SR flip-flop in its basic operation?

- 3. Describe the basic difference between pulse-triggered and edge-triggered flip-flops.

- 4. What is use of characteristic and excitation table?

- 5. What are synchronous and asynchronous circuits?

- 6. How many flip flops due you require storing the data 1101?

#### S-R Flip Flop

| <u>Dataflow Modelling</u>       | Structural Modelling                | <u>Behavioral Modelling</u>          |

|---------------------------------|-------------------------------------|--------------------------------------|

| $modulesr\_df(s, r, q, q\_n);$  | <pre>module sr_st(s,r,q,q_n);</pre> | <pre>module sr_beh(s,r,q,q_n);</pre> |

| input s, r;                     | input s, r;                         | input s, r;                          |

| output q, q_n;                  | output q, q_n;                      | output q, q_n;                       |

| assignq_n = $\sim$ (s   q);     | or g1(q_n,~s,~q);                   | regq, q_n;                           |

| assign $q = \sim (r \mid q_n);$ | or $g2(q,\sim r,\sim q_n)$ ;        | always@(s,r)                         |

| endmodule                       | endmodule                           | begin                                |

|                                 |                                     | $q,n = \sim (s q);$                  |

|                                 |                                     | assign $q = \sim (r \mid q_n);$      |

|                                 |                                     | endmodule                            |

#### T Flip Flop

<u>Behavioral Modelling</u> <u>Structural Modelling</u> <u>Dataflow Modelling</u>

```

module t_beh(q,q1,t,c);

module t_st(q,q_1,t,c);

module t_df(q,q,1,t,c);

output q,q1;

output q,q1;

output q,q1;

inputt,c;

input t,c;

input t,c;

wire w1,w2;

and g1(w1,t,c,q);

reg q,q1;

assign w1=t&c&q;

initial

and g2(w2,t,c,q1);

begin

assign w2=t&c&q1;

nor g3(q,w1,q1);

q=1'b1;

assign q=\sim(w1|q1);

nor g4(q1,w2,q);

q1=1'b0;

assign q1 = \sim (w2|q);

endmodule

end

endmodule

always @ (c)

begin

if(c)

begin

if (t==1'b0) begin q=q; q1=q1; end

else begin q=\sim q; q1=\sim q1; end

end

end

endmodule

```

# D Flip Flop

| Behavioral Modelling               | Dataflow Modelling       | Structural Modelling     |

|------------------------------------|--------------------------|--------------------------|

| Module dff_async_reset( data, clk, | module dff_df(d,c,q,q1); | module dff_df(d,c,q,q1); |

| reset ,q );                        | input d,c;               | input d,c;               |

| input data, clk, reset;            | output q,q1;             | output q,q1;             |

| output q;                          | assign w1=d&c            | and $g1(w1,d,c)$ ;       |

| reg q;                             | assign w2=~d&c           | and $g2(w2,\sim d,c)$ ;  |

| always @ ( posedgeclk or negedge   | $q=\sim(w1 q1);$         | nor g3(q,w1,q1);         |

| reset)                             | $q1=\sim(w2 q);$         | nor g4(q1,w2,q);         |

| if (~reset) begin                  | endmodule                | endmodule                |

| q <= 1'b0;                         |                          |                          |

| end                                |                          |                          |

| else begin                         |                          |                          |

| q <= data;                         |                          |                          |

| end                                |                          |                          |

| endmodule                          |                          |                          |

|                                    |                          |                          |

# JK Flip Flop

#### Post lab

- 1. Discuss the application of flip-flops in data storage.

- 2. Draw the logic diagram of Master Slave JK flip-flop.

- 3. A flip-flop is presently in the RESET state and must go to the SET state on the next clock pulse. What must J and K be?

- 4. What do you know about clk and clk event in VERILOG?

- 5. Convert the following.

- a. JK to T f/f

- b. SR to D

- 6. Write the VERILOG code for question no 5.

#### Lab Report

Each individual will be required to submit a lab report. Use the format specified in the "Lab Report Requirements" document available on the class web page. Be sure to include the following items in your lab report:

Lab cover sheet with staff verification for circuit diagram

Answer the pre-lab questions

Complete paper design for all three designs including K-maps and minimized equations and the truth table for each of the output signals.

Answer the post-lab questions

## Grading

Pre-lab Work 20 points

Lab Performance 30 points

Post-lab Work 20 points

Lab report 30 points

For the lab performance - at a minimum, demonstrate the operation of all the circuits to your staff incharge

The lab report will be graded as follows (for the 30 points):

VERILOG code for each experiments

15 points

Output signal waveform for all experiments and its truth table

15 points

#### **EXP 6: COUNTERS**

#### Introduction

The purpose of this experiment is to introduce the design of Synchronous Counters. The student should also be able to design n-bit up/down Counter.

#### **Software tools Requirement**

Equipments:

Computer with Modelsim Software

Specifications:

HP Computer P4 Processor – 2.8 GHz, 2GB RAM, 160 GB Hard Disk

Softwares: Modelsim - 5.7c, Xilinx - 6.1i.

#### **Algorithm**

STEP 1: Open ModelSim XE II / Starter 5.7C

STEP 2: File -> Change directory -> D:\<register number>

STEP 3: File -> New Library -> ok

STEP 4: File -> New Source -> Verilog

STEP 5: Type the program

STEP 6: File -> Save -> <filename.v>

STEP 7: Compile the program

STEP 8: Simulate -> expand work -> select file -> ok

STEP 9: View -> Signals

STEP 10: Select values -> Edit -> Force -> input values

STEP 11: Add -> Wave -> Selected signals -> Run

STEP 12: Change input values and run again

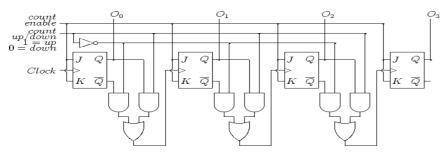

# **Logic Diagram**

Figure 6.3.1 Updown Counter

# **PreLab questions**

- 1. How does synchronous counter differ from asynchronous counter?

- 2. How many flip-flops do you require to design Mod-6 counter.

- 3. What are the different types of counters?

- 4. What are the different types of shift registers?

- 5. How many f/fs are needed for n-bit counter?

- 6. What is meant by universal shift register?

## **VERILOG Program**

# **Up Down Counter**

```

moduleupdown(out,clk,reset,updown);

output [3:0]out;

inputclk,reset,updown;

reg [3:0]out;

always @(posedgeclk)

if(reset) begin

out<= 4'b0;

end else if(updown) begin

out<=out+1;

end else begin

out<=out-1;

end

```

endmodule

#### **Post Lab questions**

- 1. Write the use of enable and reset signal.

- 2. What is the function of generic statement?

- 3. Design mod-6 counter using d flf and write the VERILOG code.

## Lab Report

Each individual will be required to submit a lab report. Use the format specified in the Lab

Report Requirements document available on the class web page. Be sure to include the following items in your lab report:

Lab cover sheet with staff verification for circuit diagram

Answer the pre-lab questions

Complete paper design for all three designs including K-maps and minimized equations and the truth table for each of the output signals.

Answer the post-lab questions

#### **Grading**

Pre-lab Work 20 points

Lab Performance 30 points

Post-lab Work 20 points

Lab report 30 points

For the lab performance - at a minimum, demonstrate the operation of all the circuits to your staff incharge

The lab report will be graded as follows (for the 30 points):

VERILOG code for each experiments 15 points

Output signal waveform for all experiments and its truth table 15 points

#### **EXP 7:** BITWISE OPERATORS USING 8051

#### Introduction

The purpose of this experiment is to implement bitwise operators using 8051. The student should also be able to implement Logical Operations in 8051.

## **Software tools Requirement**

Equipments:

Computer with Keil µversion II Software

Specifications:

HP Computer P4 Processor – 2.8 GHz, 2GB RAM, 160 GB Hard Disk

Softwares: Keil µversion II

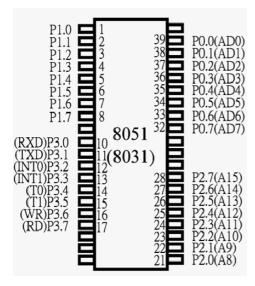

# Pin Description of 8051

#### Pre lab questions

- 1. Write an 8051 C program to toggle bits of P1 continuously forever with some delay.

- 2. What is the use of Watchdog timer?

- 3. What is sbit, sbyte?

- 4. What is DPTR?

- 5. What is Power ON Reset?

# **Embedded C Program**

```

#include<reg51.h>

void main()

unsigned int z;

P0=0x35&0x04;

P1=0x35|0x04;

P2=0x35^0x04;

P3 = -0x04;

for(z=0;z<=50000;z++);

P0=0x35>>0x04;

P1=0x35<<0x04;

p1 - µVision3 - [D:\ssss\bit.c]

File Edit View Project Debug Flash Peripherals Tools SVCS Window Help

Project Workspace

01 #include<reg51.h>

23

Parallel Port 0

void main()

Register

Value

02

03⊡ {

Port 0

04 unsigned int z;

P0: 0x03 7 Bits 0

P0=0x35&0x04;

r1

0x00

P1=0x35|0x04;

Pins: 0x00

P2=0x35^0x04;

08

P3=~0x04;

0x00

for (z=0; z<=50000; z++);

23

Parallel Port 1

0x00

10

P0=0x35>>0x04:

Port 1

P1=0x35<<0x04;

11

12

P1: 0x50 7 Bits 0

∃ Sys

13

Pins: 0x50

23

Parallel Port 2

Port 2

PC $

C:0x51...

P2: 0x31 7 Bits 0

1850475

states

1.8504.

sec

Pins: 0x31

Parallel Port 3

Disassembly

bit.c

Pins: 0xFB VVVVVVV

Running with Code Size Limit: 2K

```

#### Post lab:

- 1. Design a Calculator using 8051.

- 2. Write the Embedded C Program for the above.

- 3. Write the Embedded C Program for Bit Operations.

## Lab Report

Each individual will be required to submit a lab report. Use the format specified in the "Lab Report Requirements" document available on the class web page. Be sure to include the following items in your lab report:

Lab cover sheet with staff verification for circuit diagram

Answer the pre-lab questions

Complete paper design for all three designs including K-maps and minimized equations and the truth table for each of the output signals.

Answer the post-lab questions

#### **Grading**

Pre-lab Work 20 points

Lab Performance 30 points

Post-lab Work 20 points

Lab report 30 points

For the lab performance - at a minimum, demonstrate the operation of all the circuits to your staff incharge

The lab report will be graded as follows (for the 30 points):

Embedded C code for each experiments 15 points

Output signal for all experiments and its model calculation 15 points

#### **EXP 8:** TOGGLE A PORT BIT IN 8051

#### Introduction

The purpose of this experiment is to Toggle a Port bit in 8051. The student should also be able to control Port Pin in 8051.

## **Software tools Requirement**

Equipments:

Computer with Keil µversion II Software

Specifications:

HP Computer P4 Processor – 2.8 GHz, 2GB RAM, 160 GB Hard Disk

Softwares: Keil µversion II

#### Pre lab questions

- 1. Write an 8051 C program to toggle bits of P1 continuously forever with some delay.

- 2. What is the use of Watchdog timer?

- 3. What is sbit, sbyte?

- 4. What is DPTR?

- 5. What is Power ON Reset?

# **Embedded C Program**

```

#include<reg51.h>

sbit Mybit=P1^0;

void main()

{

while(1)

{

unsigned int z;

Mybit=0;

for(z=0;z<=5000;z++);

Mybit=1;</pre>

```

```

for(z=0;z<=5000;z++);

p1 - µVision3 - [D:\ssss\tog.c]

<u>File Edit View Project Debug Flash Peripherals Tools SVCS Window Help</u>

→ 44 件 ← → 128 巻 20 ← → 件 44  <del>-</del>

Project Workspace

01 #include<reg51.h>

02 sbit Mybit=P1^0;

Register

Value

03 void main()

Parallel Port 1

04 - {

r0

0x00

Port 1

while (1)

0x00

05

P1: 0xFF 7 Bits 0

06

0x00

unsigned int z;

07

-- r3

0x00

Pins: 0xFF VVVVVV

08

09

10

Mybit=0;

r4

0x00

for(z=0;z<=5000;z++);

0x00

Mybit=1;

r6

0x00

for(z=0;z<=5000;z++);

r7

0x00

12

13

Sys

0x00

14

0x00

dptr

0x0000

PC $

C:0x08.

states

389

0.0003..

sec

0x00

```

#### Post lab:

- 1. A door sensor is connected to the P1.1 pin, and a buzzer is connected to P1.7. Write an 8051 C program to monitor the door sensor, and when it opens, sound the buzzer. You can sound the buzzer by sending a square wave of a few hundred Hz.

- 2. Write an 8051 C program to get the status of bit P1.0, save it, and send it to P2.7 continuously.

#### Lab Report

Each individual will be required to submit a lab report. Use the format specified in the "Lab Report Requirements" document available on the class web page. Be sure to include the following items in your lab report:

Lab cover sheet with staff verification for circuit diagram

Answer the pre-lab questions

Complete paper design for all three designs including K-maps and minimized equations and the truth table for each of the output signals.

Answer the post-lab questions

# **Grading**

Pre-lab Work 20 points

Lab Performance 30 points

Post-lab Work 20 points

Lab report 30 points

For the lab performance - at a minimum, demonstrate the operation of all the circuits to your staff incharge

The lab report will be graded as follows (for the 30 points):

Embedded C code for each experiments 15 points

Output signal for all experiments and its model calculation 15 points

#### **EXP 9: DELAY OPERATORS IN 8051**

#### Introduction

The purpose of this experiment is to introduce delay operators 8051. The student should also be able to write ISR for various Interrupts in 8051.

## **Software tools Requirement**

Equipments:

Computer with Keil µversion II Software

Specifications:

HP Computer P4 Processor – 2.8 GHz, 2GB RAM, 160 GB Hard Disk

Softwares: Keil µversion II

# Pre lab questions

- 1. Write an 8051 C program to gets a single bit of data from P1.7 and sends it to P1.0.

- 2. What is ISR?

- 3. Name the two ways to access Interrupts?

- 4. What is Power ON Reset?

# **Embedded C Program**

```

#include<reg51.h>

void todelay(void)

{

TMOD=0x01;

TL0=0x08;

TR0=1;

TH0=0xEF;

}

void main()

{

```

```

while(1)

P1=0xAA;

todelay();

} }

p1 - μVision3 - [D:\ssss\delay.c]

File Edit View Project Debug Flash Peripherals Tools SVCS Window Help

曾 😅 🖬 🎒 & 鸭 晶 | 오오 | 車車 16 % % % % 🐃 [

<u>-</u> #4 #4 ← → (<u>10</u> / (a) | (a) | (b) | (b) |

Project Workspace

01 #include<reg51.h>

02

void todelay(void)

Register

Value

03⊟ {

23

Regs

Parallel Port 1

TMOD=0x01;

TL0=0x08;

rO

0x00

04

Port 1

05

0x00

TR0=1;

P1: 0xAA

06

r2

0x00

0x00

07

THO=OxEF;

r3

Pins: 0xAA

08 -}

0x00

r4

09

void main()

r5

0×00

10 - {

r6

0x00

11 while (1)

0x00

12

Sys

P1=0xAA;

< 13

0x00

todelay();

14

0x00

15

0x07

Sp

16

0x07

sp_max

0x0000

dptr

PC S

C:0x08.

states

389

0.0003.

sec

+ psw

0x00

```

#### **Postlab:**

- 1. A door sensor is connected to the P1.1 pin, and a buzzer is connected to P1.7. Write an 8051 C program to monitor the door sensor, and when it opens, sound the buzzer. You can sound the buzzer by sending a square wave of a few hundred Hz.

- 2. Write an 8051 C program to get the status of bit P1.0, save it, and send it to P2.7 continuously.

#### Lab Report

Each individual will be required to submit a lab report. Use the format specified in the "Lab

Report Requirements" document available on the class web page. Be sure to include the following items in your lab report:

Lab cover sheet with staff verification for circuit diagram

Answer the pre-lab questions

Complete paper design for all three designs including K-maps and minimized equations and the truth table for each of the output signals.

Answer the post-lab questions

# **Grading**

Pre-lab Work 20 points

Lab Performance 30 points

Post-lab Work 20 points

Lab report 30 points

For the lab performance - at a minimum, demonstrate the operation of all the circuits to your staff incharge

The lab report will be graded as follows (for the 30 points):

Embedded C code for each experiments 15 points

Output signal for all experiments and its model calculation 15 points